Creo que lo que le falta a este howto es desarrollar el punto 5. A a eso me he dedicado últimamente y voy a compartirlo con vosotros.

Hasta ahora, yo tenía la idea de que sin un programador específico, no era posible programar la FPGA de manera permanente, puesto que al usar un fichero .bit, este sólo afecta al chip FPGA y por tanto, al apagar, vuelve a su estado inicial.

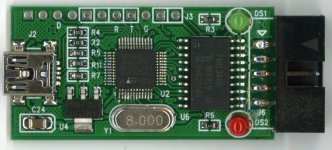

Como sabréis, la manera de conseguir esto es programando la flash ROM de la placa, pero no parecía posible con este tipo de adaptadores. Yo lo he conseguido programando la FPGA mediante ficheros SVN, lo cual nos permitirá acceder a su flash ROM y así hacer los cambios de forma permanente.

Aunque se menciona expresamente la Pano Logic G1, es fácilmente aplicable a cualquier FPGA soportada por el software ISE de Xilinx. La versión utilizada ha sido la 14.7 para Linux 64, aunque en principio nada indica que no se pueda hacer igual con una versión igual o superior para Linux o Windows.

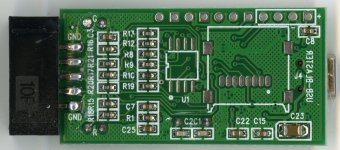

En primer lugar abrimos el ISE y si no hemos generado aún el fichero .bit, tendremos que obtenerlo del siguiente modo:

1) Sintetizarlo (Synthetize - XST).

2) Generar el fichero .bit (Generate Programming File).

Ahora ya podemos ir a la utilidad IMPACT para programar la FPGA (aunque realmente no lo haremos, sólo generaremos ficheros .SVF), haciendo doble click a Configure Target Device:

En IMPACT vamos a hacer lo siguiente: doble click en Boundary Scan para seleccionar el fichero .bsd correspondiente a la definición de nuestra FPGA. Para una Spartan 6, está en el siguiente directorio: $XILIN_HOME/14.7/ISE_DS/ISE/spartan6/data

Dentro de cada modelo, podemos encontrar packages diferentes. Si desconocemos este dato, con seleccionar el fichero base es suficiente.

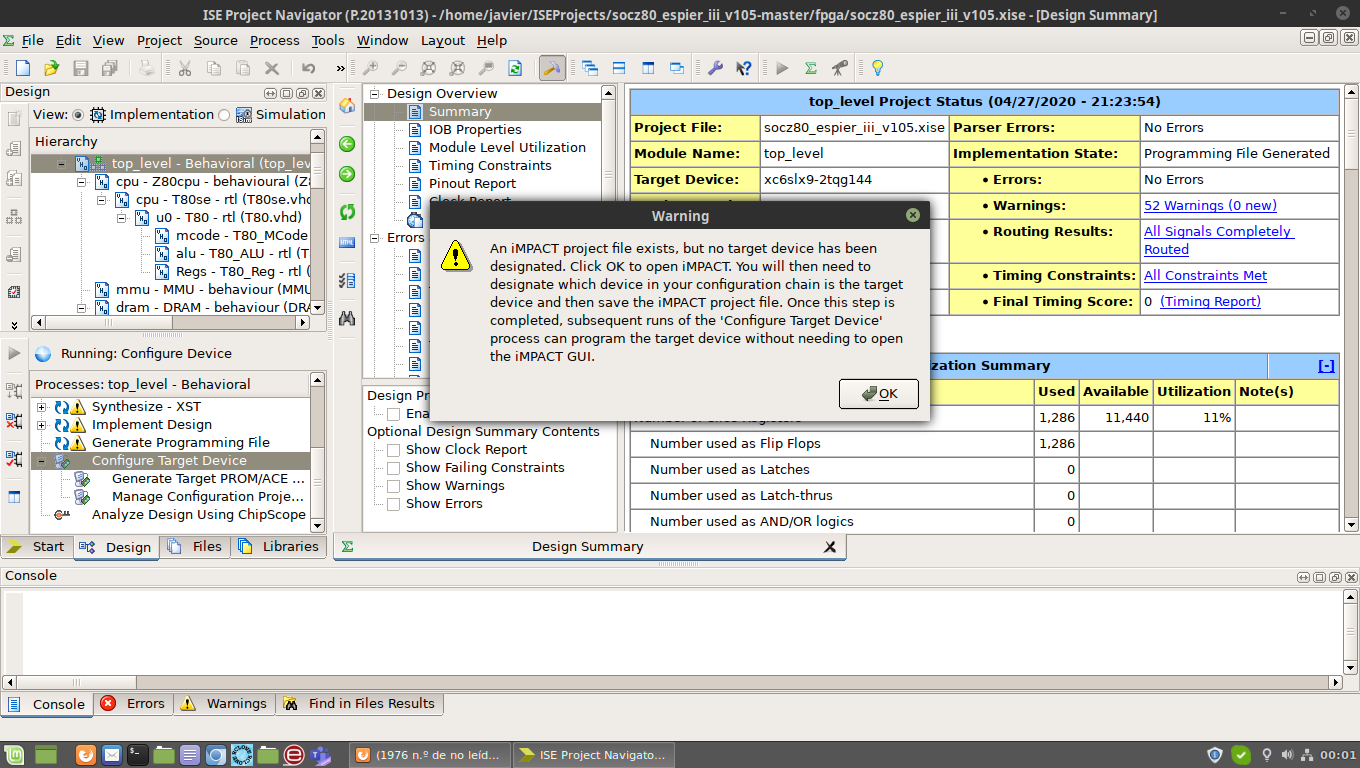

Ahora nos vamos a Create PROM File y hacemos doble click. Se nos abre una ventana donde definiremos el fichero MCS con las características de nuestra flash ROM en la que almacenaremos el diseño sintetizado: básicamente es el tipo de flash, tamaño (en bits) y nombre del fichero.

Al finalizar esto, se nos ofrece un diálogo para selecionar el .bit que hemos obtenido en ISE. Seleccionamos el .bit y a la izquierda ya podremos darle a Generate File...

Solo queda volver al Boundary Scan para, con el botón derecho, seleccionar el fichero MCS con la definicion de la flash ROM, generado anteriomente. Ahí también podremos especificar con más detalle el tipo de PROM de nuestra FPGA.

Ahora es cuando ya podemos generar los ficheros finales que usaremos para programar la FPGA. Tendremos que aplicar los siguientes, por orden:

- Uno para borrar la FPGA; lo llamaremos erase.svf.

- Otro para programarla, llamado program.svf.

Para generar el primero, en el diagrama de Boundary Scan, selecionaremos el dibujo de la memoria flash y nos vamos al menú Output -> SVF File -> Create SVF File y ponemos erase.svf.

Luego otra vez en el diagrama de la flash, con botón derecho Set Erase Properties. Aquí elegimos las dos opciones full que aparecen.

Nos vamos abajo a la izquierda y hacemos doble click en "Erase", lo cual provocará que se genere el fichero. Nos vamos al menú Output -> SVF File -> Stop Writing file.

Ahora vamos a por el otro fichero. Es similar, solo que pondremos como fichero program.svf y las propiedades que editaremos son las correspondientes a Set Programming Properties, donde desactivaremos la verificación (Verify) y el borrado previo (Design-Specific Erase Before). Para generar el fichero, haremos doble click en Program.

No olvidar cerrar el fichero program.svf, dirigiéndonos al menú Output -> SVF File -> Stop Writing file.

Por último, utilizaremos esos ficheros para programar la flash ROM mediante la herramienta urjtag:

Código: Seleccionar todo

$ jtag

jtag> cable usbblaster

Connected to libftdi driver.

jtag> detect

IR length: 6

Chain length: 1

Device Id: 00100100000000000001000010010011 (0x24001093)

Manufacturer: Xilinx (0x093)

Part(0): xc6slx9 (0x4001)

Stepping: 2

Filename: /usr/local/share/urjtag/xilinx/xc6slx9/xc6slx9

jtag> svf erase.svf progress

jtag> svf program.svf progress

jtag> quit

$

SI todo ha ido bien, cada vez que encendamos la placa, la FPGA se programará con el contenido de la flash ROM.

Bibliografía:

Enlaces: